* i-THOPおよびDLLは新光電気工業㈱の登録商標です。

* i-THOPおよびDLLは新光電気工業㈱の登録商標です。

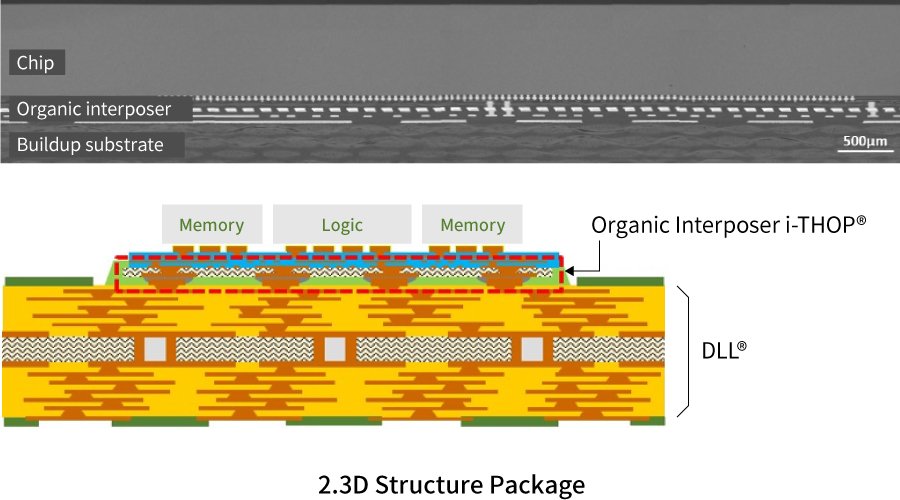

ヘテロジニアス構造の半導体パッケージの実現のため、実装技術が担う役割が近年ますます高まってきています。

新光電気は、狭ピッチフリップチップ実装技術とそれを応用とした最先端の実装技術を用い、Beyond5G、6Gの世界を実現する半導体パッケージのアセンブリソリューションを提案します。

次世代半導体パッケージのアセンブリ技術として、先端技術の開発を進めています。

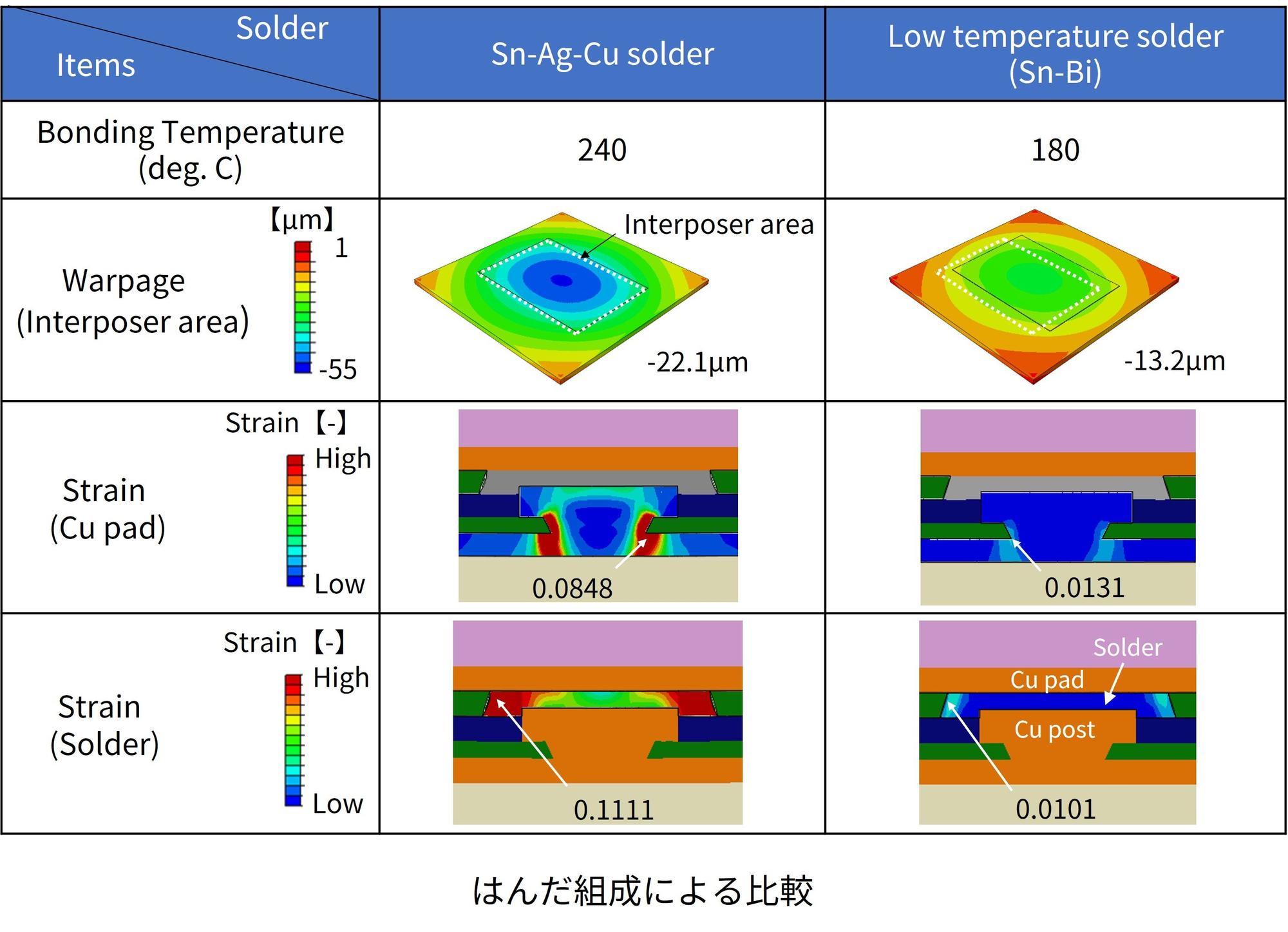

1. “2.3D有機インターポーザの開発”、坂口勇太 塚本晃輔 三木翔太 加治木篤典、 Mate2023 (29th Symposium on Microjoining and Assembly Technology in Electronics).

2. “有機インターポーザを用いた高密度基板”、三木翔太、 坂口勇太、塚本晃輔、加治木篤典、エレクトロニクス実装学会誌 Vol.26 No.4 (2023).

3. “Development of Chip-last Ultra Large Organic Package”, Kyota Yamamura, 12thIEEE CPMT Symposium Japan (ICSJ2023).

4. “Demonstration of 2.3D Organic Package with Increased Interposer Size and Layer Count”, Kosuke Tsukamoto, Wataru Kaneda, Masayuki Mizuno, Manabu Nakamura, Yuta Yamazaki, Koyuki Kawakami, Yoshihiro Kobayashi, and Atsunori Kajiki, The 20th International Symposium on Microelectronics and Packaging (ISMP2022).

5. “Development of High Reliability Joint of Sn-Bi Solder for 2.3D Organic Package”, Shota Miki, Koyuki Kawakami, Kei Murayama and Kiyoshi Oi, ICEP (International Conference on Electronics Packaging) 2021.

6. “Effect of crystal anisotropy and IMCs on electro-migration resistivity of low temperature flip chip interconnect”, Kei Murayama, Mitsuhiro Aizawa, Kiyoshi Oi, ECTC (IEEE Electronic Component and Technology Conference) 2021.

7. “Environmental load reduction technology using low-temperature solder for high-performance semiconductor packages”, Kei Murayama, Mitsuhiro Aizawa and Kiyoshi Oi, Electronics Goes Green 2020+.